This article introduces the cache of stm32, including icache and dcache, and briefly introduces how cache can help optimize the performance of stm32. The article also includes structural pictures for reference. Let's read on.

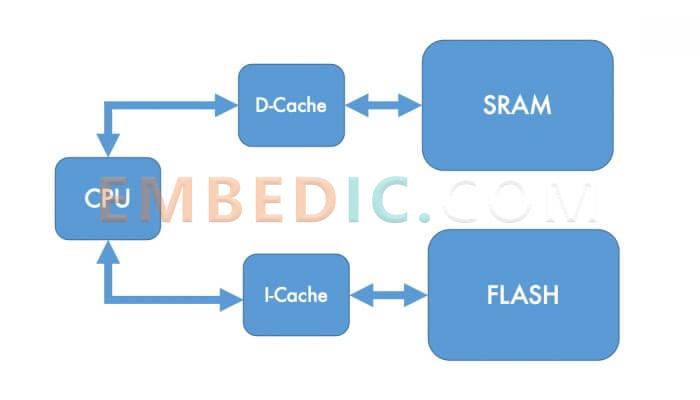

Cache is cache memory, iCache (instructions cache) is the instruction cache memory, dCache (data cache) is the data cache memory.

The basic law of storage media is that the faster the read and write speed per unit of storage capacity, the higher the price, in order to balance the storage speed and price, the computer's use of hierarchical storage system, according to the read and write speed from fast to slow: CPU -> registers -> cache -> memory -> external memory.

Among them, registers are integrated into the Soc internal, directly interact with the CPU data, the number is limited; in a higher performance computer, cache is possible to use multi-level; memory is generally RAM, external memory can be disk, flash, etc..

The icache and dcache are cache, icache is used to cache instructions and dcache is used to cache data. icache and dcache are used to improve system performance.

For example, the CPU can only process one instruction at a time, if it finishes executing an instruction to fetch an instruction from memory, the CPU will read memory frequently, but the speed of memory is much smaller than the execution speed of the CPU, which will limit the CPU's operation speed.

With icache, the instructions to be executed and the instructions adjacent to the instruction can be read into icache at one time and cached, so that when the instruction is to be executed, the CPU can first look for it in icache and then read it from memory if it is not found. The same principle applies to dcache, which caches the most recently used data. This involves the principle of spatial locality and temporal locality of the program.

The ICACHE and DCACHE introduced in the AHB bus of the Arm Cortex-M33 processor are embedded in the STM32 microcontrollers (MCUs) listed in the table below.

These caches enable the user to improve application performance and reduce power consumption when fetching instructions and data from internal and external memory or when data traffic is used for external memory. This document provides typical examples to highlight the ICACHE and DCACHE functions and to facilitate configuration.

This section provides an overview of the ICACHE and DCACHE interfaces embedded in STM32 Arm Cortex core-based microcontrollers. The ICACHE and DCACHE block diagram architectures and their integration in the system architecture are described in detail.

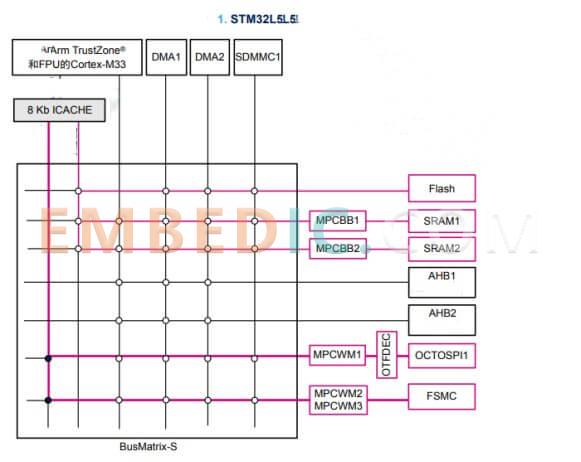

This architecture is based on a bus matrix that allows multiple master devices (Cortex-M33, DMA1/2 and SDMMC1) to access multiple slave devices (e.g. Flash memory, SRAM1/2, OCTOSPI1 or FSMC).

The following figure depicts the STM32L5 family smart architecture.

Due to the introduction of the 8-Kb ICACHE interface to its C-AHB bus, the performance of the Cortex-M33 is improved when fetching code or data from internal memory (Flash memory, SRAM1 or SRAM2) via the fast bus or from external memory (OCTOSPI1 or FSMC) via the slow bus.

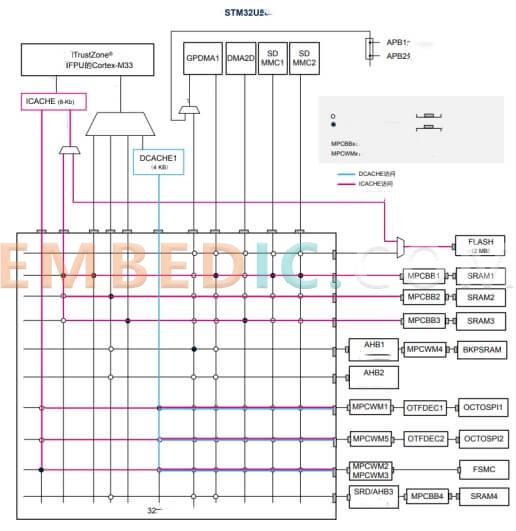

This architecture is based on a bus matrix that allows multiple master devices (Cortex-M33, GPDMA1, DMA2D and SDMMC1/2) to access multiple slave devices (e.g. Flash memory, SRAM1/2/3/4, BKPSRAM, OCTOSPI1/2 or FSMC).

The following diagram depicts the STM32U5 family smart architecture.

Its C-AHB bus introduces the 8-Kb ICACHE interface, which improves the performance of the Cortex-M33 when fetching code or data from internal memory (Flash memory, SRAM1, SRAM2 or SRAM3) via the fast bus or from external memory (OCTOSPI1, OCTOSPI2 or FSMC) via the slow bus. Its S-AHB bus introduces a 4-Kb DCACHE interface, which improves the data flow from external memory (OCTOSPI1, OCTOSPI2 or FSMC).

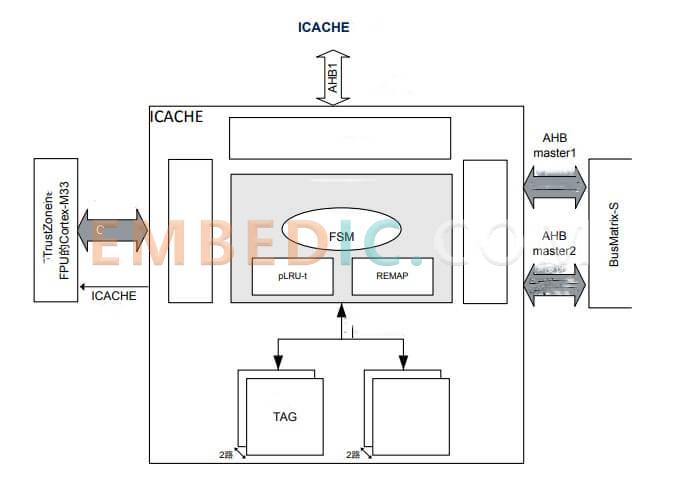

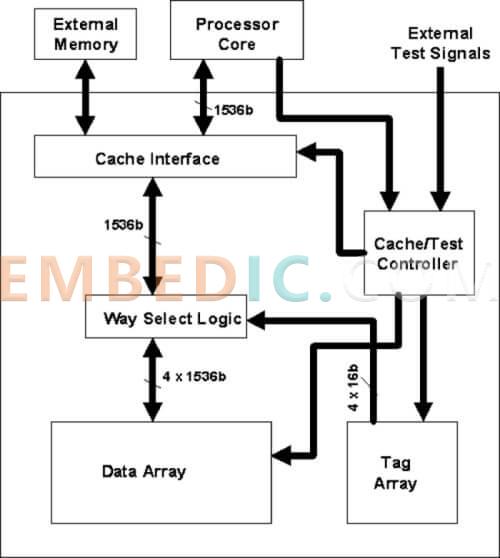

The ICACHE block diagram is shown in the following figure.

ICACHE memory includes.

- A TAG memory with the following elements.

- Address labels indicating which data to include in the cache data memory

- Valid bits

- Data memory containing the cached data

The DCACHE block diagram is shown in the following figure.

DCACHE memory consists of

- TAG memory with the following elements.

- Address labels indicating which data to include in the cached data memory

- valid bits privileged bits

- dirty bits

- Data memory containing the cached data

Manufacturer: Microchip

IC MCU 32BIT 32KB FLASH 28QFN

Product Categories: 32bit MCU

Lifecycle:

RoHS:

Manufacturer: Microchip

IC MCU 8BIT 14KB FLASH 44QFN

Product Categories: 8bit MCU

Lifecycle:

RoHS:

Manufacturer: Texas Instruments

IC DSP 181CPGA

Product Categories: DSP

Lifecycle:

RoHS:

Manufacturer: Texas Instruments

IC DGTL MEDIA PROCESSR 1031FCBGA

Product Categories: DSP

Lifecycle:

RoHS:

Looking forward to your comment

Comment