System-on-a-chip (soc) is increasingly becoming a network where you can add individual intellectual property (IP) modules. SoC IP blocks include processors, memory controllers, dedicated subsystems and I/O-these blocks can be separated from the interconnection IP and placed in increasingly complex SoC partitions. In the near future, when electronic systems are allowed to make decisions, more and more complex SoCs are required.

The interconnection has to deal with various communications within the SoC, which is an efficient IP module integration mechanism. Interconnection is the most configurable IP within the SOC—usually it will be changed many times during a project, and it is almost always changed between different projects. It also plays an important role in information security and functional security, because it carries most of the SoC data, and contains almost all SoC internal long-term connections and system-level services, including quality of service (QoS), visibility , Physical perception and power management. The interconnection can achieve multi-processor SoC cache coherence, improve the performance and bandwidth of advanced driver assistance system (ADAS) automotive chips and network SOCs, and can achieve ultra-low power consumption in long-running consumer devices.

Connected IP must continue to evolve to promote the application of innovative SoCs in emerging industries, such as the emerging artificial intelligence (AI) and machine learning (ML) applications, which are driving innovation in data center automation and autonomous driving.

As process dimensions continue to shrink, soc interconnects have become more critical. Dividing the chip into functional circuit modules with reusable IP, or "chiplets", can not only improve the yield of the die, but also add more functions to the current 16-nanometer and below process. With the Chiplet integration method, developers can integrate bare chips developed by multiple companies or chips with specific functions (such as memory and I/O) into a single package.

The size of the interconnect is usually about 10% of the entire SoC, but it will significantly affect the quality, performance and delivery schedule of the SoC. Compared with the overall budget of the SoC, the initial licensing cost of interconnection IP is relatively small, but "inefficient" interconnection may cause process, cost, and specification issues. For example, if the interconnect cannot close the timing at the set target performance, the SoC will not be able to meet the frequency specification, which may cause the design to fail.

The high-performance interconnection IP used in multiple SoC projects needs to meet a variety of standards, including:

Architecture flexibility - The interconnection must adapt to various topologies to achieve the necessary flexibility. For example, the interconnection architecture must have a tree structure (most suitable for heterogeneous SoC) and conventional topologies, including grid, ring, and circular (required by AI and network SoC). Interconnect IP must also be able to "extend down" to meet the low-end interconnection requirements of projects such as IP subsystems and SoC service interconnections.

For example, an interconnection with only corner router switching may be suitable for high-end networks, but not for mobile SoCs, where minimization of power consumption, area and delay is very important. On the other hand, the lack of corner router switching is not conducive to the delivery of high-end server designs or artificial intelligence/machine learning accelerators. Similarly, interconnects that can handle non-correlated communications but do not support cache coherency will limit the choice of cache coherent SoC architecture. The protocol conversion function means that the interconnection can support various IP module communication protocols, and can maximize the IP modules selected in the design.

●Frequency-If the interconnection cannot reach the target frequency, it will limit the performance of the SoC. For example, if the processor runs at 4 GHz and the cache coherent interconnect cannot run at 2 GHz, performance will be limited. However, not all paths in the SoC are the same. It is essential to have multiple frequency domains and rate adaptation capabilities, so that each path can run at different frequencies. After all, why pay for the high-performance path for the entire interconnect when there are only a few paths that need to run at the highest specified frequency?

● Delay—The delay is determined by the number of cycles required for the data packet from the start-up program to the target IP module. It depends on the efficiency of the interconnection IP, the length of the line to the destination, and the physical location of the interconnection IP function. Interconnect physical perception is very important in the process technology of 16nm and below, because the timing closure must be estimated as early as possible in the RTL (register transfer level) stage to avoid problems in the placement and routing stage.

There is a trade-off between delay and frequency: if the frequency is high, more pipes are needed, which will increase the delay. For latency-sensitive processor-to-memory paths, minimizing latency is especially important. The good news is that there are relatively few paths in SoCs that have demanding delays, but keep in mind that the additional delay cycles on these paths usually become system-level SoC performance constraints. The longer the path, the more wires are used to generate the path, and more pipes must be added to meet timing constraints. The network-on-chip (NoC) interconnection uses distributed switching, which usually has lower latency than the hybrid bus mode that uses centralized crossover. Distributed arbitration further shortens the path between switching units. Not all networks are delay critical, so interconnections should provide flexibility for high-latency paths, such as I/O IP blocks that are only used during the initial operation of the SoC. In SoC design, the path capability with high delay can save wiring.

●Bandwidth/throughput—Bandwidth is the maximum rate of data transmission on a given path. Throughput refers to the amount of data successfully transmitted along the interconnection path. Throughput may be limited by the interconnection architecture, implementation topology, and packet protocol. Efficient interconnection can make performance as close to the theoretical bandwidth as possible; inefficient interconnection will cause bottlenecks. An interconnect that can support 8-bit low-bandwidth connections to 1024-bit high-bandwidth connections—and the width of the interconnection between the two—provides designers with the most flexible architecture.

Area-Silicon is a cost factor in any SoC design. A useful metric is that, according to the 16nm process standard, the cost of 1 square millimeter of silicon in each SoC is usually 10 cents. The use of fewer wires and gates and more efficient interconnect topologies can save costs. If the area can be reduced by more than 5 square millimeters, the output will increase and additional costs can be saved. Because area-efficient interconnects usually account for about 10% of the SoC area, the interconnect area is reduced by 30-50%, and the chip-level SOC can save a few square millimeters of silicon. Roughly speaking, an interconnect with high area efficiency will save about 3-5 square millimeters on a 100 square millimeter SoC, and each SoC will save 30-50 cents, depending on the production efficiency.

Power-In stand-alone consumer or Internet of Things (IoT) devices, power consumption is essential. In the active power mode, the interconnection IP consumes less power than the CPU and GPU, but these can be shut down quickly when the task is completed. In fact, for most battery-powered systems, standby power consumption is the determinant of battery life. When there is no data communication but the clock is on, proper management of interconnect power consumption is critical to idle power consumption (or standby power consumption).

For battery-powered systems that are in idle mode most of the time, a low-power interconnect is required. This interconnection IP must implement a power control strategy through a three-level clock gate, so that multiple power domains can be easily created, a power domain can be started in one cycle, and low-power domain crossover can be realized. For 16nm interconnect power consumption, a reasonable metric is that the idle power consumption per million interconnected logic gates is less than 0.5mW.

Functional safety-critical applications must comply with strict safety standards, such as the ISO 26262 standard in the automotive market. In order to meet the requirements of ASIL (Automotive Safety Integrity Level) B, C and D in ISO26262, the interconnection IP implementation requires flexible functions to compensate for system-level and random errors and achieve the required fault detection and protection levels. To meet the highest level of ASIL D, interconnection IP requires logical replication of network interface units, ECC (error correction code) and/or parity bit data path protection, and data packet integrity checking. The interconnection IP supplier must also be able to provide functional safety manuals, as well as corresponding analysis and operating data, to prove that the interconnection IP is suitable for use in systems that comply with the ISO26262 standard. Without such documents and operating data, it is difficult to identify semiconductor components in the final electronic system.

Information security-functional safety and reliability can protect SOC from manufacturing and environmental errors, while information security can protect critical chips from human attacks. An effective interconnection must be able to implement a firewall, which is usually configured by the design team. When data is transferred from one area of the SoC to another area, the area isolation function must be provided to achieve security. These interconnected hardware features should be seamlessly integrated with the entire system-level security scheme and enhance its security.

Productivity—Efficient interconnect tools can accelerate deployment and improve the predictability of the SoC design process. Internet IP software tools should include:

SoC requirements and target input for customers, markets, and design intent.

Design exploration of architecture optimization.

Multi-level modeling function of early SOC and interconnection analysis.

Generate interconnect RTL for various SoC topologies.

Physical perception of early timing closure estimates.

Automatic function verification for NoC verification in time.

On-chip observability and debugging to achieve SOC visibility.

Automatic FMEDA output, in line with ISO 26262 standard, can accelerate functional safety analysis.

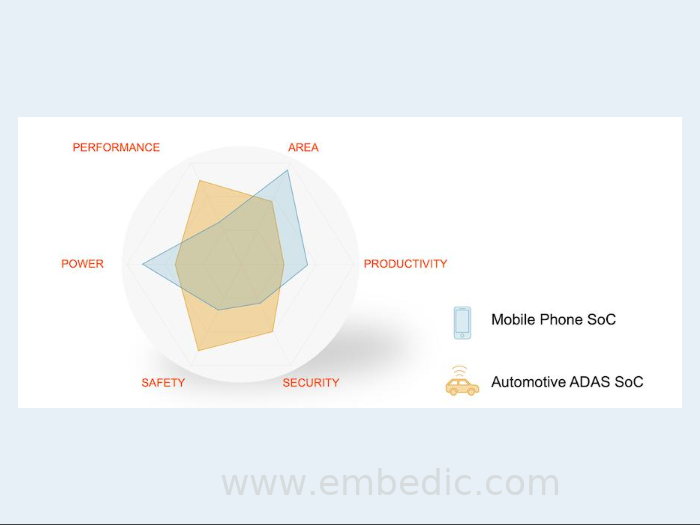

figure 1. On-chip interconnects must meet the different requirements of various types of chips.

The ecosystem of IP and electronic design automation (EDA) products means supporting multiple IP protocols from companies such as ARM, Synopsys, and Cadence. It also means integration with simulation, simulation, verification, functional safety, modeling, and layout routing tools from leading and start-up EDA vendors. World-class interconnect production efficiency software and integration with other IP and EDA tools can reduce SoC project development costs and schedule time.

IP cost calculation

Although the interconnection IP only accounts for 10% of the SoC area, it may cause delays and even miss the system design window. The best case is that sub-optimal SoC may cause timing problems, cause deadlocks that prevent SoC operation, cause data scarcity, bandwidth bottlenecks, and lack of functionality in the SoC subsystem, which will increase the development costs of unforeseen solutions. And delay. Therefore, high-performance and proven interconnections play a vital role in the success of SoC design projects.

in conclusion

The development of high-efficiency interconnected IP requires years of hard work, which may cost between 70 million and 100 million US dollars. Taking shortcuts can lead to disappointment and cost a lot of business costs. Designing interconnects for a single chip is a challenge, but providing a broad interconnect solution suitable for multiple SoC designs requires capital, scale, and commitment. Assembling and retaining IP teams may encounter challenges. They must be interdisciplinary talents (architects, hardware engineers, software developers, and verification engineers), and maintain cooperation for many years during the development project.

Effective interconnection makes it easier and more predictable to deliver complex SoCs, while reducing design costs. The SoC project director only needs to select the appropriate interconnect.

Manufacturer: Analog Devices

IC DSP 16BIT 600MHZ 289CSBGA

Product Categories: 16bit DSP

Lifecycle:

RoHS:

Manufacturer: Texas Instruments

IC DSP FIX PT 16BIT LP 196NFBGA

Product Categories: 16bit DSP

Lifecycle:

RoHS:

Manufacturer: Microchip

IC MCU 8BIT 1.5KB OTP 8SOIJ

Product Categories: 8bit MCU

Lifecycle:

RoHS:

Manufacturer: Analog Devices

IC DSP CTRLR 16B W/CODEC 289BGA

Product Categories: 16bit DSP

Lifecycle:

RoHS:

Looking forward to your comment

Comment